# United States Patent [19]

# Reed et al.

[11] Patent Number:

4,575,924

[45] Date of Patent:

Mar. 18, 1986

## [54] PROCESS FOR FABRICATING QUANTUM-WELL DEVICES UTILIZING ETCH AND REFILL TECHNIQUES

[75] Inventors: Mark A. Reed, Dallas; Robert T. Bate, Garland, both of Tex.

[73] Assignee: Texas Instruments Incorporated, Dallas, Tex.

[21] Appl. No.: 626,809

[22] Filed: Jul. 2, 1984

[51] Int. Cl.<sup>4</sup> ...... H01L 21/203; H01L 21/302; H01L 29/161

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,626,257 | 12/1971 | Esaki et al   | 148/DIG. 169 |

|-----------|---------|---------------|--------------|

| 4,103,312 | 7/1978  | Chang et al   | 357/16       |

| 4,194,935 | 3/1980  | Dingle et al  | 148/175      |

| 4,257,055 | 3/1981  | Hess et al    | 357/16       |

| 4,261,771 | 4/1981  | Dingle et al  | 148/175      |

| 4,450,463 | 5/1984  | Chin          | 357/16 X     |

| 4,503,447 | 3/1985  | Iafrate et al | 357/16       |

|           |         |               |              |

## FOREIGN PATENT DOCUMENTS

59-31071 2/1984 Japan ...... 357/22 MO

#### OTHER PUBLICATIONS

Vojak et al., "Low-Temperature-Quantum-Well Al-

GaAs—Deposition" J. Appl. Phys., 50(9) Sep. 1979, pp. 5830-5834.

Vojak et al., "Tunnel-Injection—Quantum-Well Al-GaAs—Deposition, Ibid., 50(9) Sep. 1979, pp. 5835-5840.

Ralls et al., "Discrete Resistance Switching—Noise" Physical Rev. Lett., vol. 52, No. 3, Jan. 16, 1984, pp. 228-231.

Lebwohl et al., "Electrical Transport Properties in a Superlattice" J. Appl. Phys., vol. 41, No. 6, May 1970, pp. 2664–2667.

TSU et al. "Nonlinear Optical Response—Electrons in a Superlattice" Appl. Phys. Lett., vol. 19, No. 7, Oct. 1, 1971, pp. 246–248.

Chang et al., "Resonant Tunneling in Semiconductor Double Barriers" Appl. Phys. Lett., vol. 24, No. 12, Jun. 15, 1974, pp. 593-595.

Sollner et al., "Resonant Tunneling Through Quantum Wells—" Appl. Phys. Lett., vol. 43(6) Sep. 15, 1983, pp. 588-590.

Primary Examiner—William G. Saba Attorney, Agent, or Firm—Carlton H. Hoel; Robert O. Groover; James T. Comfort

#### [57] ABSTRACT

The present invention teaches a process for fabrication of quantum-well devices, in which the quantum-wells are configured as small islands of GaAs in an AlGaAs matrix. Typically these islands are roughly cubic, with dimensions of about 100 Angstroms per side. To fabricate these, an n- on n+ epitaxial GaAs structure is grown, and then is etched to an e-beam defined patterned twice, and AlGaAs is epitaxially regrown each time. This defines the quantum wells of GaAs in an AlGaAs matrix, and output contacts are then easily formed.

20 Claims, 37 Drawing Figures

Fig.4

ELECTRODE NO.3

SELF-CONSISTENCY DIAGRAM; 2nd TO LAST LAST TRAP **EXCITED STATES** 2 3 TO GND STATE J NOT L 4 Fig.16

Fig.19

# THIS TRUTH TABLE IS

В (C) CAN BE O OR 1 !

Fig.31

Fig.34

Fig. 35

Fig. 36

## PROCESS FOR FABRICATING QUANTUM-WELL DEVICES UTILIZING ETCH AND REFILL **TECHNIQUES**

#### BACKGROUND AND SUMMARY OF THE **INVENTION**

The present invention relates to a process for fabricating quantum-coupled electronic devices.

It is generally recognized that conventional VLSI integrated technical technology will be prevented from further scaling by the time MOS devices get down to a quarter micron channel length, and perhaps even at much larger geometries. Since much of the advance in integrated circuit capabilities has been based on the continued progress of scaling, this near-future barrier is of substantial concern.

Thus it is an object of the present invention to provide an integrated circuit technology wherein active 20 devices can have active regions smaller than one quarter micron in dimension.

It is further object of the present invention to provide an integrated circuit technology wherein active devices can be fabricated which occupy a total area of less than 25 <sup>1</sup>/<sub>4</sub> of a square micron average for each active device.

A further inherent limitation of conventional integrated circuit technology is speed. MOS devices have inherent limits on their speed due to the channel-length transmit time. Integrated bipolar devices also have in- 30 herent speed limitations, due to the base width transit time, and are also likely to have high power dissipation.

Thus it is an object of the present invention to provide an active device having higher potential maximum speed than any MOS device.

It is a further object of the present invention to provide an active device which is potentially faster than any bipolar device.

It is a further object of the present invention to provide an active device which is potentially faster than 40 any bipolar device, and which also has a very low power dissipation.

To achieve these and other objects, the present invention provides: a new genus of electronic devices, (e.g. islands of GaAs in an AlGaAs lattice) are made small enough that at least two components of momentum of carriers within the wells are discretely quantized. This means that, when the bias between the wells is adjusted to align energy levels of the two wells, tun- 50 neling will occur very rapidly, whereas when energy levels are not aligned, tunneling will be greatly reduced. This high-gain mechanism leads to useful electronic device functions.

However, these devices are exceedingly difficult to 55 fabricate, due to their extremely small dimensions. In particular, for the embodiments which are capable of high temperature operation (i.e. room temperature or liquid nitrogen temperature operation), the geometries required must be even smaller yet. In addition, it is 60 using moderately large wells, wherein the upper-lying necessary to fabricate these extremely small geometry wells in such a manner that very good interface quality will be preserved at the boundaries of the wells.

Thus it is an object of the present invention to prowherein quantum wells with maximum dimensions less than 500 Angstroms and with extremely good interface quality can be fabricated.

It is a further object of the present invention to provide a process for fabrication of quantum-well devices. wherein quantum wells with maximum dimensions less than 500 Angstroms and with extremely good interface quality can be fabricated, wherein contacts for coupling to the quantum wells are also fabricated.

It is a further object of the present invention to provide a process for fabrication of quantum-well devices. wherein quantum wells with maximum dimensions less than 150 Angstroms and with extremely good interface quality can be fabricated, wherein contacts for coupling to the quantum wells are also fabricated.

According to the present invention there is provided: A process for fabricating quantum-well devices, comprising the steps of:

providing a substrate;

providing first and second epitaxial layers of a first semiconductor material on said substrate;

said first layer being doped to a concentration of at least 1E17 per cubic centimeter and being at least 200 nm thick.

and said second layer comprising a dopant concentration no greater than 5E16 per cubic centimeter and a thickness less than 300 Angstroms;

anisotropically etching trenches in a first pattern through said second layer but not entirely through said first layer;

epitaxially growing a second semiconductor material, which has a wider bandgap than said first semiconductor material and is approximately lattice-matched to said first semiconductor material, to substantially fill said trenches;

anisotropically etching trenches in a second pattern 35 through both said first layer and said second layer into said substrate:

epitaxially growing said second semiconductor material, to substantially fill said second trenches; and

forming metallization to configure a desired circuit function;

wherein said first and second patterned trench etches jointly define a plurality of quantum wells within isolated portions of said second layer,

and wherein said second trench etch defines interconwherein at least two closely adjacent potential wells 45 nections of said quantum wells within said first layer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will be described with reference to the accompanying drawings, wherein:

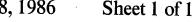

FIGS. 1A and 1B show spacing and energy levels of potential wells in a simple sample embodiment;

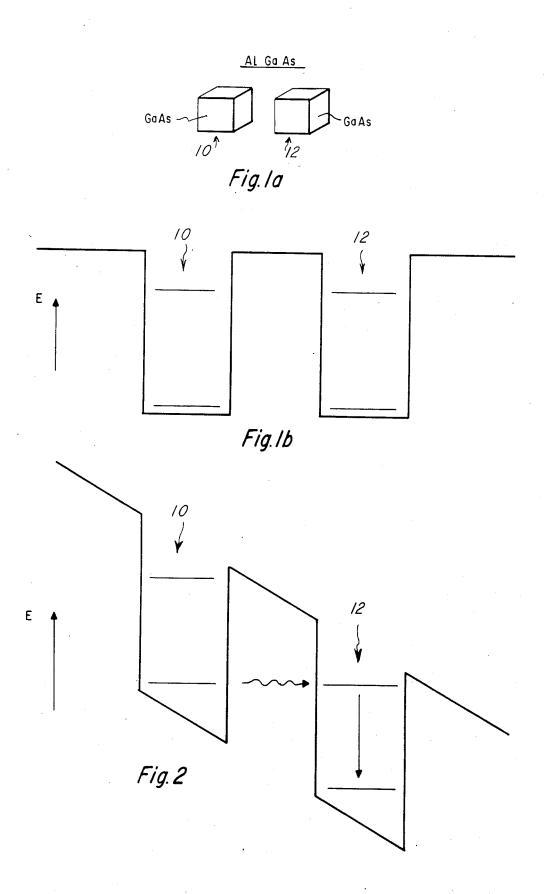

FIG. 2 shows the structure of FIG. 1, biassed to permit resonant tunnelling;

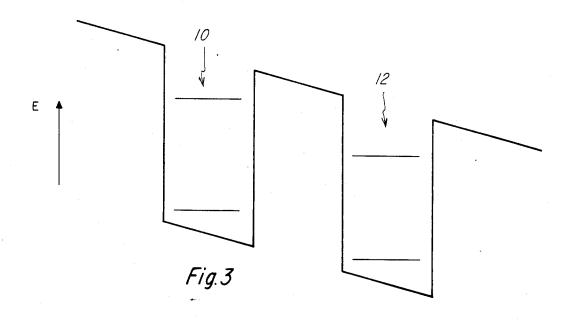

FIG. 3 shows the structure of FIG. 1, biassed at a lower voltage than shown in FIG. 2, so that resonant tunnelling is forbidden;

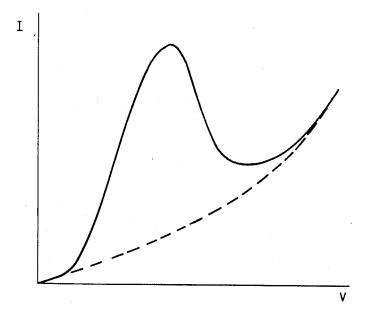

FIG. 4 shows voltage-current characteristics of the structure of FIG. 1;

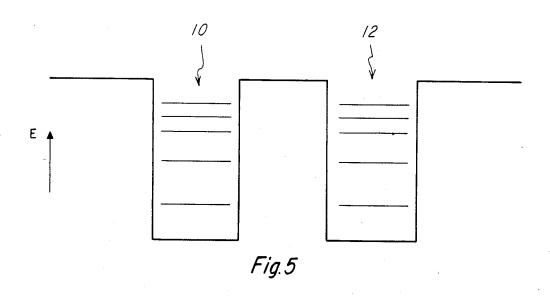

FIG. 5 shows the energy levels of an embodiment energy levels are more closely spaced;

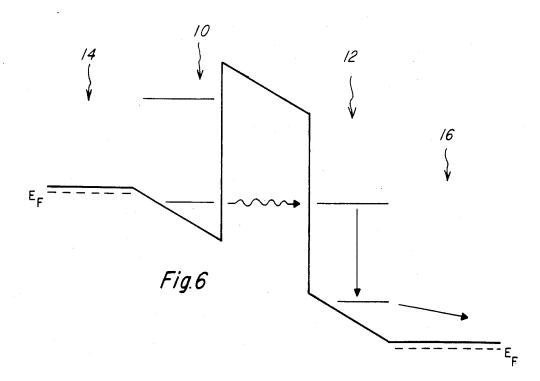

FIG. 6 shows the electronic structure of an embodiment including input and output contacts;

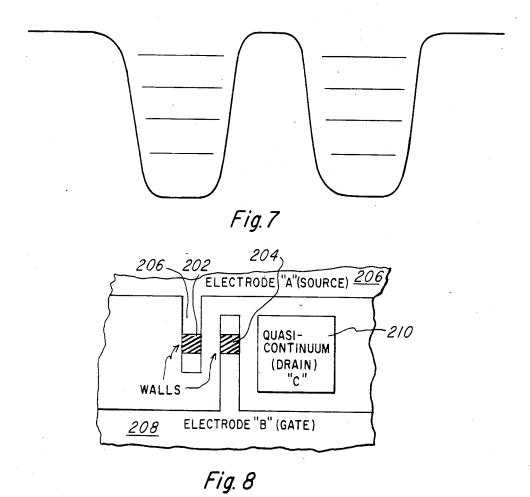

FIG. 7 shows the energy levels of an embodiment vide a process for fabrication of quantum-well devices, 65 using approximately sinusoidal well boundaries, wherein the energy levels are more equally spaced;

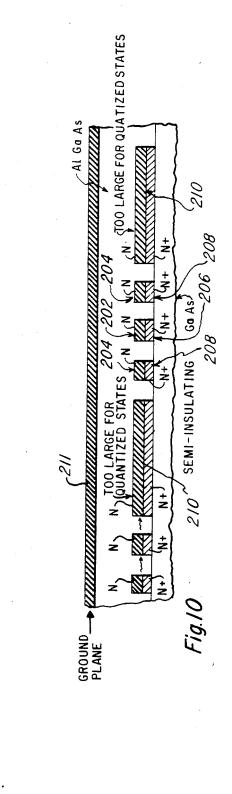

> FIG. 8 shows a three-terminal quantum-well device according to the present invention;

T,3/3,72

FIG. 9 shows another three-terminal quantum-well device according to the present invention, wherein multiple chains of quantum-well pairs are connected in parallel;

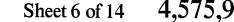

FIG. 10 shows a cross-section of the device of FIG. 5 9:

FIG. 11 shows a many-terminal device, which differs from the device of FIG. 9 in having multiple electrodes 208 prime for connection to multiple wells 204 prime in each chain;

FIG. 12 shows a sample set of bias conditions for the embodiment of FIG. 11 wherein resonant tunnelling occurs, and FIG. 13 shows a sample set of bias conditions for the embodiment of FIG. 11 wherein resonant tunnelling does not occur;

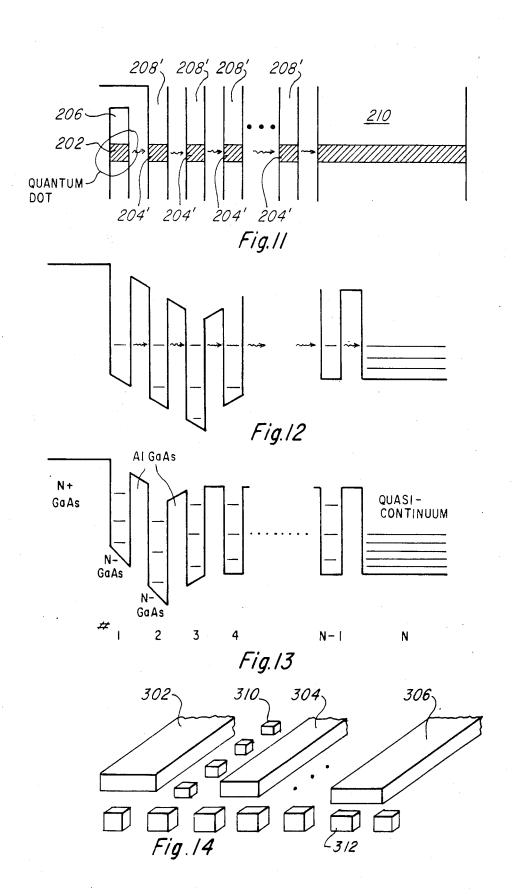

FIG. 14 shows a read-only memory according to one embodiment of the invention;

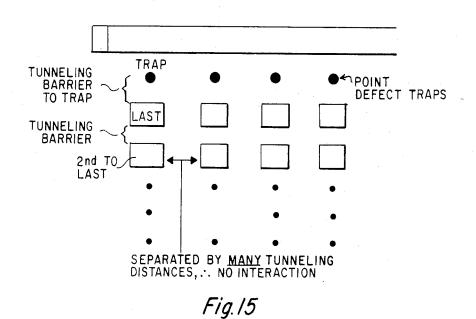

FIG. 15 shows a sample output switch configuration used in practicing the present invention, wherein quantum-well devices switch macroscopic output currents; 20

FIG. 16 shows the effect of the electric potential change induced by the population of well levels on the permissible tunnelling transitions in a further class of embodiments;

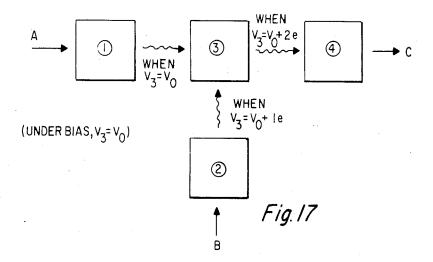

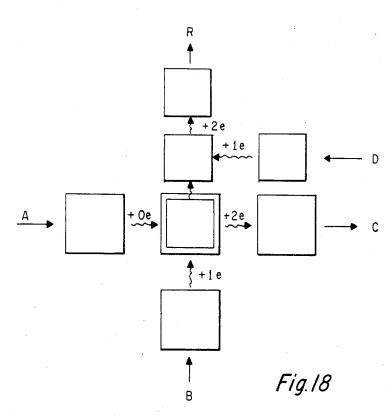

FIG. 17 shows an AND gate configured using quan- 25 tum-well logic with self-consistent tunnelling restrictions, and FIG. 18 shows a more complex logic element configured using quantum-well logic with self-consistent tunnelling restrictions;

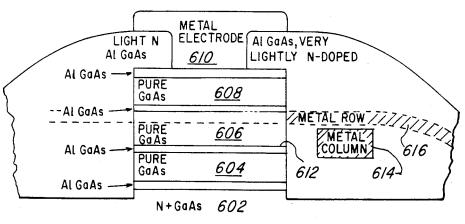

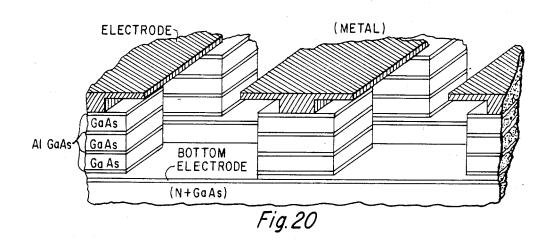

FIGS. 19 and 20 show two embodiments of verticaltunnelling quantum-well device structures according to the invention; and

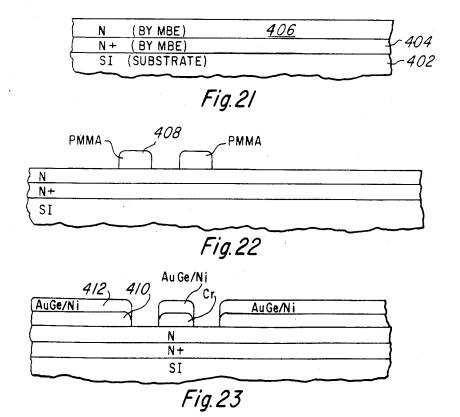

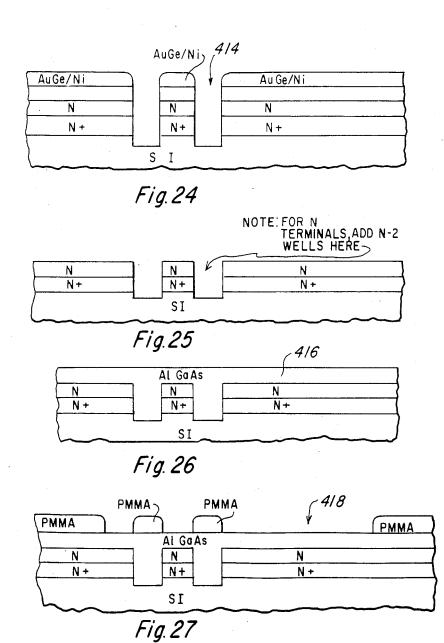

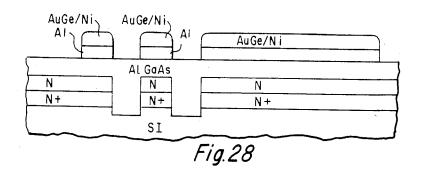

FIGS. 21-36 show steps in processing a sample three-terminal device according to the present invention.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

The present invention teaches active devices which are fundamentally different from the transistor and diode structures which have been used heretofore in the 40 electronics industry to configure integrated circuits. That is, active devices taught by the present invention are neither field effect transistors nor bipolar transistors, but operate according to principles which are fundamentally and entirely different.

A key feature of many embodiments of the invention is a pair of closely coupled quantum wells which are each extremely small, so small that their electron populations are quantized, i.e. an electron in a well can only have one of a few allowable energies. The present invention teaches modes of device operation which cannot be analyzed by classical physics, but must be understood in light of quantum mechanics.

Advances in semiconductor processing now permit semiconductor structures to be patterned with exceedingly small dimensions, comparable to the Bloch wave length of an electron. (The Bloch wavelength measures the "width" of an electron in a semiconductor. The location of an electron must be measured by a probability distribution, which has a certain width.) The present 60 invention makes use of the availability of patterned structures in dimensions which are close to the Bloch wave length to achieve new types of device structures, capable of new principles of operation of a kind not seen before in semiconductor or integrated circuit devices. 65

A simplified sample embodiment, which demonstrates some of the key principles of operation used in the present invention, is shown in FIG. 1. Separate

wells of gallium arsenide are embedded in a matrix of aluminum gallium arsenide. As is well known in the semiconductor art, the bandgap of AlGaAs is wider than that of GaAs. (More precisely, the pseudo-binary alloys of the formula  $Al_xGa_{1-x}As$  are all semiconductors, with a bandgap which increases as a function of x.) This different bandgap means that conduction-band electrons in the lattice see a lower potential energy in the GaAs regions than in the AlGaAs regions. A particular advantage of this material system is that the interface between GaAs and AlGaAs is a very well behaved one, that is such interfaces can be fabricated with an extremely low density of surface states (less than the Si/SiO<sub>2</sub> interface), and can preserve lattice match al-15 most perfectly between the GaAs and the AlGaAs sides of the interface. However, as will be discussed below, the present invention can be practiced with a wide variety of material systems, and not only semiconduc-

In the sample embodiment of FIG. 1, the wells 10 are about 125 angstroms wide, and the spacing between the wells is also about 125 angstroms. The dimensions of these wells are small enough that the energy states of electrons in the well will be quantized. That is, these wells are preferably made cubic, and the allowable energy states of an electron in a cubic well of such dimensions can be calculated easily, using the effective mass approximation for the behavior of the electron, as a simple particle in a box problem in quantum mechanics. Thus, for example, for the well dimensions given above, and an aluminum concentration of 35%, there exist four allowable energy states, and the lowest lying energy state will be above the bottom of the GaAs conduction band minimum and will be separated from the next lowest energy state by 0.070 electron volts. The next higher lying energy state will lie another 0.114 electron volts higher. Note that these energy states must be treated as quantized. That means that the energy of an electron in the well must be exactly equal to one of these permitted discrete energy levels and cannot take any other value. This is key to the present invention. Note that this is a fundamental difference from normal semiconductor devices (even from the advanced semiconductor devices projected to be achievable by scaling present semiconductor devices), in that all conventional solid state devices—be they field effect or bipolar transistors or anything else—require that the energy levels of an electron within the conduction band of the semiconductor be quasi-continuous.

It should be noted that the number of electrons which can populate each energy level in such a quantized system is strictly limited. That is, the lowest lying energy level in each well in this example can be populated by only two electrons, the next level up can be populated by only six electrons, the next level up can be populated by only ten electrons, and so on. This means that the number of carriers within a well is strictly limited. Thus, a carrier cannot tunnel to an energy state in the next well if that energy state is already completely filled. While each well can hold only a few carriers at a time, it should be noted that the transition times are expressly short (typically far less than a pico-second), and total current can be increased by operating many pairs of wells in parallel.

Now, in the sample embodiment the wells are placed sufficiently close such that the probability density of an electron in one well extends into the neighboring well; that is, the wells 10 and 12 in FIG. 1 are close enough

6

together that electrons can tunnel between them easily. In particular, as shown in FIG. 1b, an electron in the first well can tunnel easily to a state of equal energy in the second well, but of course it cannot do this unless an unoccupied state having the same energy actually exists 5 in the second well. However, suppose that the energy levels in the two wells do not line up. Then an electron in the first well can only tunnel to states of the second well which have a different energy than the first well, and it can only tunnel to such states if there is also some 10 mechanism whereby the electron can lose or gain enough energy to reach the energy of the lower-lying available state in the second well.

The chief mechanism for the changing of the energy of an electron to achieve tunnelling in this fashion is 15 relaxation via surface states. That is, even the GaAs to AlGaAs interface, which is exceedingly benign as semiconductor interfaces go, will have a measurable density of surface states at the interface. Such surface states provide a scattering process which will permit an elec- 20 tron to transfer to higher or lower energy, if it intersects one of the available sites for scattering. That is, the interface can be described as having an areal density of scattering sites which are capable of changing the energy from an electron so that it can make the transition 25 between wells even when the energy levels of the wells do not line up. This mode of transition is known as inelastic tunneling. The alternative mode of tunneling, wherein the electron tunnels from the first well to the second with no change in energy, is known as resonant 30 tunneling.

Tunneling requires conservation both of energy and also of momentum. Momentum is also quantized for small potential wells. That is, in each dimension of the box which defines the boundaries of the potential well, 35 mentum but not energy are quantized, i.e. closely the smaller the length of that dimension the more widely spaced the allowable values of that component of momentum will be. Thus, as reported in the Soloner et al. article cited below, resonant tunneling can occur between two very closely spaced thin sheets of lower 40 ing background controlled. That is, if a scattering cenpotential. Since the potential wells are very large in two dimensions, the momentum components in those two dimensions are not quantized. That is, when one dimension of a potential well is large, the momentum components in that direction are so closely spaced that a back- 45 ground lattice phonon will be available to supply the momentum difference. That is, the density of phonons found in the lattice follows Bose-Einstein statics, i.e. the number of phonons found in the lattice at energy E in a background lattice temperature T varies as 1 over (EXP 50 ((E/k T)-1)). This energy distribution of phonons also implys a distribution for the magnitude of momentum of the phonons, and, since the phonons can be treated as approximately isotropic in reasonable semiconductor materials, this same distribution also specifies the distri- 55 ling will not be increased comparably, since as noted bution of phonons having a desired value of some one particular component of momentum. Thus, the quantization of momentum in a potential well can be considered as discrete or quasi-continuous only in relation to temperature. That is, for example, a 1000 angstrom wide 60 box will result in momentum quantization at one degree Kelvin, since the phonon population will be crowded into energetically low states, but at 300 K there would be a tremendous lattice background phonon population to bridge gaps between the allowable momentum val- 65 ues, and thus the separation between the allowable momentum values in this direction would not be meaningful, i.e. momentum in this direction would have to be

treated as a quasi-continum value, i.e. any value of this momentum component which an incoming carrier had would still permit tunneling, since lattice phonons could adjust this momentum component to one of the allowable values. If all three components of momentum are discretely quantized, then it follows that energy must be discretely quantized also. The quantization of energy levels is (to a rough approximation) merely dependent on the volume of the potential well, so that a thin flat potential well could have quantized energy states and sharply separate discrete allowable levels for one component of momentum, whereas the allowable values of the other two momentum components will be closely spaced, so that they impose no practical constraint on tunneling.

That is, the resonant tunneling gain is enhanced in accordance with the number of parameters which must be met. In tunneling between two closely spaced cubic potential wells, all three components of momentum (and therefore energy) must match between the state which the carrier is leaving in the first well and the state which the carrier is entering in the second well. That is, if an incoming carrier does not satisfy all three momentum constraints, the chances of it finding a lattice phonon which has exactly the right components to satisfy the difference in each of the three momentum values is quite small. However, if only one component must be adjusted, the chances of accidentally doing this by interaction of the lattice phonon are much greater.

Thus, the preferred embodiments of the present invention use structures wherein all three components of momentum are quantized. However, a class of less preferred alternative embodiments of the present invention uses structures wherein only two components of mospaced thin wires. It is easy to satisfy the momentum constraint alone by a phonon-assisted process, but the necessity for satisfying both energy and momentum conversation is what keeps the rate for inelastic tunnelter at the metallurgical interface can change the energy of a carrier, it is easy for one of the lattice phonons to provide the appropriate adjustment in momentum.

As device dimensions are made smaller, two desirable effects are achieved: First, the separation of the quantized energy states in a well increases as the well dimension becomes smaller. Second, as the wells become closer together, the rate of tunneling is increased. That is, the probability of tunneling can be expressed as a constant times exp  $(-2d \times f(E))$ , where d is the distance between the wells and E is the energy difference.

This exponential dependance means that the probability of resonant tunneling is tremendously increased as the distance between wells is reduced. Inelastic tunnelabove inelastic tunnelling is limited, in good material, by the density of scattering centers. Thus, room temperature operation becomes possible at interwell spacing of about 125 A or less.

A limitation on resonant tunnelling is provided by thermal "smearing", i.e. redistribution of energy level populations caused by background thermal energy. That is, the density of states distribution within each well of the discrete energy levels is broadened somewhat by thermal smearing. At higher temperatures, the thermal smearing is greater. The problem thermal smearing causes is that the operating temperature must be low enough that thermal smearing does not populate

higher energy level states. That is, the electrons should reside in the lowest energy level to eliminate accidental coincidences and bidirectional elastic tunneling. This reduces to the condition that the energy spacing must be much larger than the thermal energy of the electrons. 5 Thus, for operation at 4° K. with GaAs wells in an Al<sub>0.3</sub>Ga<sub>0.7</sub>As matrix, the well width (and well spacing) should be in the neighborhood of 0.1 to 0.2 microns or less. However, to increase the operating temperature to 300° K., the critical dimension needs to be reduced 10 known physics, as reflected in these articles and pressmerely to a number on the order of 125 Angstroms or

It should be further noted that the energy levels in adjacent wells can be made to line up or not line up simply by applying a bias, as shown in FIG. 2. In this 15 which are quantized only in one dimension, which imcase, a sufficient bias voltage has been applied in the direction of conduction, so that the second level in the second well is lined up with the first level in the first well. Under these conditions resonant tunneling will regularly occur, and the fast relaxation from the second 20 level to the ground state in the second well ensures that the device is unidirectional.

If zero bias were applied to this same structure, resonant tunneling would still be possible, but would be bidirectional. That is, at zero bias the energy levels in 25 two adjacent wells will line up, but electrons will tunnel from the first well to the second well just as fast as they tunnel from the second well to the first well. Note, however, that if half as much bias as shown in FIG. 2 is applied, resonant tunneling will be forbidden (at suffi- 30 most convenient well dimensions. A more realistic enciently low temperature) and only inelastic tunneling if permissible. In this bias condition, as shown in FIG. 3, an electron can make a transition from a state in well one to an lower lying state in well two only if a scattering event also occurs, as discussed above. Thus, at small 35 dimensions, the frequency of inelastic transitions is limited by the density of available scattering sites. However, the density of scattering sites is in effect an areal density, since it arises primarily from surface states rather than from bulk defects or particles within the 40 crystal lattice. Thus, since the limiting factor is a areal density of defects, the inelastic tunneling current is relatively insensitive to the distance between wells. This means that, for good quality material, as the dimensions are scaled the resonant tunneling current increases tre- 45 time for tunneling. Thus, after a lower level has been mendously, but the inelastic tunneling current does not increase much.

The result of these phenomena is that the current-/voltage graph for tunneling between two wells looks approximately as seen in FIG. 4. That is, inelastic tun- 50 neling will supply a current which increases approximately exponentially with the applied voltage. Resonant tunneling will also supply at least one current peak added on to this curve, at a bias voltage where the energy levels of the wells line up. Thus, a regime of 55 substantial negative differential resistance is available, i.e. a millimeter diode with gain is available, as reported in Sollner et al., "Resonant Tunneling Through Quantum Wells at Frequency up to 2.5 THz," 43 Applied Physics Letters 588 (1983). (However, this article used 60 First, the input contact will fill all levels of the first well potential wells in which only one momentum component was discrete as discussed above.) Other background reference which set forth generally known physics of resonant tunneling are Chang et al., "Resonant Tunneling in Semiconductor Double Barriers," 24 65 Applied Physics Letters 593 (1974); Tsu et al., "Nonlinear Optical Response of Conduction Electrons in a Super Lattice," 19 Applied Physics Letters 246 (1971);

Lebwohl et al., "Electrical Transport Properties in a Super Lattice," 41 Journal of Applied Physics 2664 (1970); and Vojak et al., "Low-temperature operation of Multiple Quantum-Well Al<sub>x</sub>Ga<sub>1-x</sub>As-GaAs P-n Hetero Structure Lasers Grown by a Metal Organic Chemical Vapor Diposition," 50 Journal of Applied Physics 5830 (1979). These five references are hereby incorporated by reference. (It should be noted that portions of the foregoing discussion merely reflect generally

umably elsewhere, but other portions of the foregoing discussion are not generally known and do not reflect any understanding available in the prior art.)

However, the prior art has taught potential wells plies relaxed constraints on the selection rules for elastic tunneling. The preferred embodiments of the present invention have more stringent selection rules, and should (because all 3 dimensions are quantized) have dramatically more gain than the 1-D quantized devices. This invention is significantly different from the Esaki tunnel diode or 2-dimensional electron gas structures in that all three dimensions are quantized here, which imposes a constraint on the tunneling conditions much different than other structures; that is, the momentum constraint significantly depresses other than the desired elastic resonant tunneling.

The foregoing has supposed that only a few quantum levels are found in a well, but this is not correct for the ergy diagram of the levels in such a structure wherein 1000 angstrom GaAs wells are incorporated in an Al-GaAs lattice would be as shown in FIG. 5. Note that, in the familiar statics of the solution to the particle in a box problem, the successively higher energy levels are spaced progressively closer together. This means that, even when the bias voltage is such that the lowest few levels between the two wells do not line up, some of the higher lying levels are likely to. However, this is not a major problem, since the higher lying levels will typically be depopulated because of the temperature constraint mentioned previously. That is, the lifetime for relaxation from a higher lying state to an empty lower state will typically be much shorter than the typical depleted by tunneling, a higher level which has been excited in any fashion will tend to relax to the depleted lower level much faster than it will tunnel. However, this assumes that empty lower levels exist below the higher level from which tunneling is possible. This imposes a constraint on the input contact, which will now be discussed.

FIG. 6 shows the energy diagrams for a system of two coupled wells 10 and 12 plus input and output contacts 14 and 16. Note that the input and output contacts are doped, although the wells and the areas between them are preferably not. Note also that two important limitations on the well size arise from the necessities of making input contact and output contact. 10 by tunneling, up to an energy approximately equal to the Fermi level of the electrons in the doped semiconductor which provides the input contact. This means that none of the levels thus still filled up must line up with levels in the second well when tunneling is not desired. That is, if the wells are too large, they will have discrete energy states at the bottom of the well but will include densely spaced states below the Fermi level of

the input contact. This means that these densely spaced states will be filled, and therefore resonant tunneling current will be seen if any of these dense states line up with states in the second well. This means that the current gain of the device will be greatly reduced. Second, 5 all levels in the second well which are above the Fermi level of the output contact will equilibrate with the output contact, i.e. will essentially always remain filled. This is not itself a problem, since electrons can tunnel from the higher lying energy states in the second well 10 into the continuum of states which exists in the (large) output contact, but if any level in the first well lines up with one of these filled levels in the second well, that level in the first well will also remain filled. Note that the input and output contacts are preferably both de- 15 generately doped n-type.

The physical well shapes have been described as having perfectly sharp boundaries, but this is not quite realistic. That is, in good quality MBE material, the transitions will typically be smooth enough that the potential profile looks more precisely like that drawn in FIG. 7. This is actually advantageous, since the energy levels will tend to be more nearly equal spaced. That is, where the energy level spacings are more nearly equal, there is a wider range of bias conditions wherein a large number of the lower lying energy levels will not line up.

Of course, for the ultimately preferable small well dimensions, e.g. 125 angstroms, the number of states in a small number of states, there will be bias conditions under which no actual line ups exist.

Each tunneling transition described above is a transition of only a limited number of electrons for each pair of coincidental states. That is, each of the discrete en- 35 ergy levels in the quantum well can be populated by only a certain definite number of electrons. In the example discussed above, wherein the energy well has the approximate physical shape of a cube, the lowest lying level can be populated by only two electrons, and no 40 more. The next higher energy level can be populated by only six electrons, and no more. The third energy level can be populated by only 12 electrons, and no more. Most of the higher-lying levels can also be populated by only 12, although some may have a higher maximum 45 occupancy because of accidental degeneracies. Thus, it is important to note that a carrier cannot tunnel into even an allowable energy level unless that allowable energy level is not completely populated. The multiple states at each allowable energy level are distinguished 50 by other quantum numbers. That is, for example, the six electrons in a second energy level can have one of two possible states of spin, and can have one of three possible momentum vector directions. However, this distincfor understanding the present invention.

Thus, each tunneling transition can transport up to a dozen carriers for each pair of lined-up wells. More than one pair of wells may be lined up at the same time. Moreover, many pairs of wells may be operated in par- 60 read only memory. allel. Moreover, the transit time for tunnelling can be extremely small, less than a pico second. Thus, although only a few electrons are translated in each tunneling event, a reasonable current density can be achieved nevertheless.

Thus, a basic family of embodiments is structures, as described above, wherein two quantized wells separate an input contact from an output contact. However,

further aspect of the present invention provide numerous other kinds of innovative device structures.

For example, a three terminal device according to the present invention is shown in a plan view in FIG. 8. A first quantum dot 202 is coupled to a second quantum dot 204, which is coupled to an output contact 210. The dimensions of the quantum dots 202 and 204 are selected as discussed above for quantum wells, but the output contact 210 is made sufficiently large that a quasi-continuum of states is available. The quantum well 202 is coupled from beneath to an electrode 206, and the quantum well 204 is coupled from beneath an electrode 208. These are preferably degenerately doped semiconductor regions, or may be metal lines, but in any case provide the long-distance routing necessary for formation of conventional electronic circuits.

In the presently preferred version of this embodiment, the quantum wells 202 and 204 have only 2 components of momentum discretely quantized, since they 20 are directly connected to their respective electrodes. That is, the electrodes 206 and 208 can be, for example, tungsten, with a thin layer of a conventional barrier metallization optionally provided on top. The GaAs of quantum wells 202 and 204 are formed directly on top of this conductor. Preferably the electrodes 206 and 208 are n + GaAs. Optionally, a thin barrier of AlGaAs can be provided beneath each of the quantum wells 202 or 204 and above the respective contact 206 or 208. This each well will be small, e.g. 4 states per well. With such 30 through, and therefore does not prevent DC coupling barrier is sufficiently thin that it is readily tunnelled of each quantum well to its respective electrode, but even this thin a barrier would be sufficiently small to provide sufficient quantization of all 3 parameters of momentum within each of the wells 202 and 204, and thereby increase the relative resonant tunneling gain at the expense of a small increase in processing complexity and small decrease in overall current.

> A larger scale version of essentially this structure is shown in FIG. 9. This 3-terminal quantum well device can be configured with multiple chains of quantum well pairs 202, 204 in parallel, for greater current flow. Note that electrode 206 can be thought of as acting as a source, electrode 208 can be thought of as a gate electrode, and electrode 210 can be thought of as a drain electrode. Pattern 213 can be used to define the well locations 202 and 204. FIG. 10 shows a cross section of this structure, including ground plane 211.

A further variation of this structure is shown in FIG. 11. Note that additional electrodes 208 prime are used to provide longer chains of wells 202, 204 prime, 204 prime, etc., wherein resonant tunneling will occur only if the voltages on all of the electrodes 206 and 208 prime jointly satisfy one single condition (or some one of a small set of conditions). That is, FIG. 12 shows a sample tion among isoenergetic states is relatively unimportant 55 set of electrode bias conditions wherein resonant tunneling will not occur, and FIG. 13 shows a different set of bias conditions wherein resonant tunneling will occur.

This multiple-gate device is particularly useful for a

In a read only memory (ROM) embodiment, information is hard-programmed simply by changing the degree of electrical coupling of a column line to underlying quantum wells. A sample of this embodiment is shown 65 in FIG. 14. A particular advantage of this embodiment is that the patterning of the metal lines need not be exactly aligned to the pattern of the underlying quantum wells. That is, if the pitch of the metal lines can be 11

made twice or more that of the quantum wells, and the ROM will still function.

In the sample embodiment shown, column lines 302, 304, 306, etc. are overlying metal lines. Column line 302 is electrically coupled to row 310 of quantum wells, but 5 not coupled (or less well coupled) to row 312 of quantum wells. This differential coupling can be accomplished by holes cut in a field plate, or by a dielectric patterned in multiple thicknesses. A sample mode of operation of this structure is as follows: A background 10 HCl to remove the RIE masking layer 410 and 412, as potential is defined for every column (i.e., all columns fixed at ground) such that resonant tunneling occurs through each row of quantum devices 310, 312, etc. When it is desired to read out a column of cells, the column line 302 for that column is changed to some 15 However, again, metal organic CVD is an alternative different voltage. This different voltage will perturb resonant tunneling in any row to which that column line is electrically coupled, and thereby disrupt resonant tunneling in that row. In rows to which this column is not electrically coupled resonant tunneling will not be 20 disrupted. Thus, by monitoring the current in a row, the information hard-programmed into the intersection of the addressed column and the read-out row will be detected.

A sample process for fabricating quantum well de- 25 vices according to the present invention will now be described. In particular, fabrication of 3-terminal devices, as discussed above, will be used as an example.

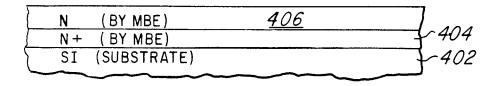

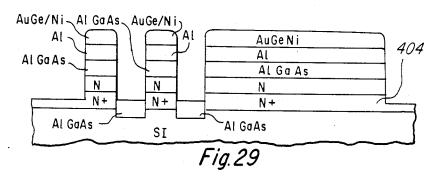

The beginning material is a semi-insulating GaAs substrate with 2 epitaxial layers. The substrate is prefer- 30 ably chromium doped, e.g. to 1015 per cubic centimeter, although this is not necessary. The first epitaxial layer is n+ GaAs. This layer will provide connections, and is therefore fairly thick and of a fairly high conductivity, e.g. 5000 angstroms thick and doped to 1018 per cubic 35 centimeter or more n type. On top of this is deposited with thin lightly doped n-type layer which will patterned to form the actual quantum wells. This layer is doped, e.g., about 1016 per cubic centimeter n-type, and, in a sample embodiment, is 150 angstroms thick. (The light 40 doping is used merely so that some carriers are available. Heavier doping would increase inelastic tunnelling). FIG. 21 shows an initial structure, having epitaxial layers 404 and 406 atop substrate 402. Optionally, as discussed above, an extremely thin layer of AlGaAs 45 could be interposed between layers 404 and 406. This structure is preferably fabricated by molecular beam epitaxy, to provide the desired sharp doping transitions. but this is not strictly necessary. Published chemical vapor deposition results, particularly using organo me- 50 tallic CVD (MOCVD), also state results of extremely sharp transitions.

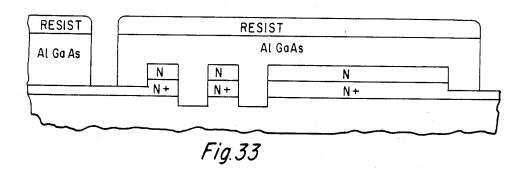

The first patterning step follows. In the presently preferred embodiment, patterning is done using electron beam with an E beam resist such as PMMA (poly- 55 methylmethacrylate). This is the presently preferred embodiment, because it provides a reliable way to make structures smaller than 0.1 microns today. Such dimensions are of course not possible using optical lithogravide a more convenient to way to do such patterning in the future. FIG. 22 shows the epitaxial structure of FIG. 21, with a patterned layer of PMMA 408 (patterned by e-beam writing and developing) in place. A reactive ion etching (RIE) mask material is then depos- 65 ited. In the presently preferred embodiment, an aluminum layer 410 and a gold/germanium/nickel layer 412 are used for this. The patterned layer 408 is then lifted

12

off, to expose only selected fine line portions of the epitaxial layer 406, as seen in FIG. 23.

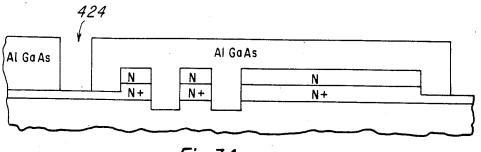

Reactive ion etching is now conventionally performed to cut trenches 414 through the epitaxial layer 406 and 404 down into the substrate 402. RIE conditions are conventionally known for such patterning, and extreme anisotropy is readily achieved at low pressure. at the expense of somewhat slow etching.

Next, the aluminum layer 410 is removed in dilute seen in FIG. 25.

Next, an AlGaAs layer 416 is epitaxially regrown overall. This fills the trenches 414. It is preferable to perform this regrowth using molecular beam epitaxy. technology. However, in any case, it is important that this regrowth be of extremely high quality, since the sidewall interface between the GaAs wells formed from layer 406 and the AlGaAs fill 416 are extremely critical, as discussed above. This regrown structure shown in FIG. 26.

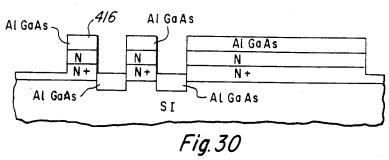

Next, a second patterning step is performed. The pattern used in this case is essentially the same pattern over the wells, but also includes the output contact in the finished structure. This pattern, seen in FIG. 27, is converted to a hard mask pattern, seen in FIG. 28, which is then reactive ion etched again. However, this reactive ion etching step has a critical depth control. It must be continued to etch into, but not through, the n+ layer 404. This critical depth control provides one reason for making the n+ layer 404 so thick, as discussed

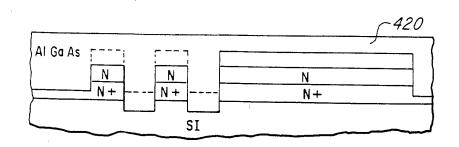

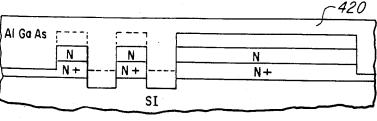

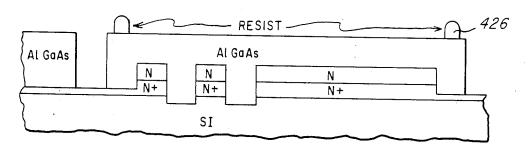

Again, the masking metal is stripped (FIG. 30), and AlGaAs is regrown overall. As discussed above, the AlGaAs needs to have a high enough percentage of aluminum to impose a significantly different conduction band energy between the AlGaAs and GaAs, but it is preferable that the aluminum percentage not be too high, to provide for the best possible GaAs to AlGaAs interface. In the presently preferred embodiment, a composition of about Al<sub>0.3</sub>Ga<sub>0.7</sub>As is used. FIG. 31 shows the resulting structure, with the new AlGaAs layer 420. Note that, in FIG. 30, some portions of the AlGaAs layer 416 survive, and these portions are incorporated in the layer 420. Again, the layer 420 must be epitaxial grown with extremely good interface quality.

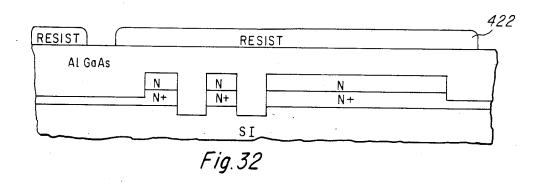

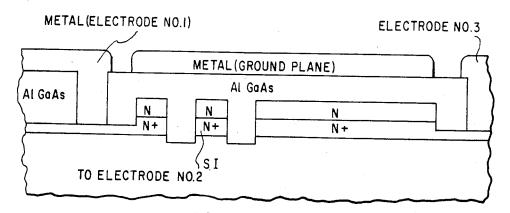

A contact metallization pattern is then applied, as shown in FIG. 32. The geometries are less demanding at this step and optical resist 422 with optical patterning is preferably used. A selective etch is then used, which will etch through AlGaAs and stop on n+ GaAs. Hydrogen fluoride has this property. This step provides contact holes 424, as seen in FIG. 34. Metallization patterning is then applied, again preferably using an optical resist 426, as seen in FIG. 35, and metal (such as AuGe/Ni) is then deposited, e.g. by evaporation, and lift off patterned, resulting in the structure as shown in

A very similar fabrication technique can be used to phy, although x-ray or ion beam lithography may pro- 60 fabricate quantum well array structure, e.g. for ROMs, simply by performing the second patterning step (shown in FIG. 27) to define linear patterns at right angles to linear patterns defined by the first patterning step, so that the intersection of the two defines locations of the quantum well dots.

A basic difficulty in interconnecting quantum well devices according to the present invention to form random logic circuit is their electrical characteristics.

These devices may be considered to have very high input impedance and very low output impedance. In a further aspect of the present invention, a circuit structure for output coupling is described which permits the output of quantum well devices according to the present invention to switch macroscopic currents, i.e. currents comparable to those normally used in integrated circuit wiring. These macroscopic currents can then be used to change electric potentials and thereby switch further stages of quantum well devices.

It is known in the prior art that macroscopic resist changes can be detected in a very thin wire due to trapping of a single electron onto a trap at or near the interface of the wire to the substrate. See the K. Raals et al. paper in 52 Phys. Rev. Letters 228 (1984). That is, in extremely small metal wires, e.g. 100 Angstroms by 100 Angstroms, the cross section of a scattering center which is close to the wire will change by many orders of magnitude depending on whether an electron is or is 20 not trapped in the scattering center. This tremendous change in scattering causes a net change in the resistance of the wire.

This effect need not be limited to wires of such small dimension. By using multiple trapping sites (scattering 25 centers), the resistance of a larger wire can be similarly modulated. In particular, where a thin or wide wire is used, a dielectric with traps coated over the surface of the wire can substantially modulate the wires resistance plish charging of the traps, a field plate is preferably used, which provdes a bias normal to the surface of the wire. Thus, the current output of a quantum well device stage (which would of course normally include multiple quantum well chains in parallel) can be coupled into a 35 thin flat wire, while a field plate bias is applied vertically to assist charge injection from the wire over the energic barrier into trapping sites in the dielectric. The charges thus trapped will modulate the resistance of the wire after the vertical bias is removed and the current 40 signal through the wire can then be used to trip a sense amplifier. Thus, this scattering center modulation in effect provides a latch suitable for conversion of the quantum well output signals to macroscopic signals.

detail. First, the dimensions of the wire next to the scattering site must be such that the wire is in what is known as the Anderson localization regime: the wave function of the electron must significantly overlap the entire periphery of the wire, i.e. all four faces of a square wire. In this regime, the resistance will be extremely sensitive to surface states adjacent to the wire. There will typically be many unintentionally generated surface states, but these normally have low activation energy. Thus, the operating temperature is selected so that these unwanted surface states will boil off readily, i.e., selected such that kT is comparable to or larger than the activation energy of these parasitic surface states, but such that the activation energy of the surface 60 states in which charges to be trapped to effect modulation is more than several times as much as kT. Thus, the principle application of this output amplifier stage is believed to be for devices operating at temperatures in the neighborhood of 77 kelvin, i.e. liquid nitrogen tem- 65 peratures. However, higher operating temperatures can be used if carriers can be injected into deeper surface states.

The surface states used in the presently preferred embodiment are about 20 to 30 meV or more removed from the conduction band energy of the metal.

Operation in the Anderson localization regime means that the dimensions of the wire close to the scattering center cannot possibly be greater than 500×500 angstroms, and are preferably closer to 100×100 angstroms. For a 100×100 angstrom wire, the resistance of the wire is roughly 100K to one megohm per micron. 10 Each scattering center which is populated or depopulated can impose a resistance change of a percent or so, and by using several such scattering centers, a total resistance change of 5% or so is achieved. Thus, these metal lines are used in pairs, and a change in current of 15 a few percent is easily enough to trip a conventional sense amplifier.

The presently preferred embodiment for accomplishing carrier injection into these traps is to have the trapping site connected to the last well in a chain of quantum wells by tunneling, i.e., the separation from the trapping site to the last well in the chain should be removed from the trapping site by no more than a few times the distance between wells, and preferably less. Tunneling out of the trap into the last well is not a limitation in the preferred embodiment since the electron enters the trap through excited states. The reverse tunneling is only inelastic. However, for a sufficiently deep trap, the required phonon energy becomes so large that the inelastic tunneling is negligible. The trapping as the traps are populated and depopulated. To accom- 30 site can be written with extreme precision using a focused ion beam.

> Thus, the configuration of this output stage is shown in FIG. 15.

As mentioned, one-way well coupling is optionally used to assist injection of carriers into these traps, to modulate the metal lines resistance. This one-way coupling is made possible by the self-consistant tunneling effects of the wells. That is, in addition to the factors discussed above, the presence or absence of electrons in the wells will itself modulate the electric field between wells. Thus, as shown in FIGS. 16A and B, the change in electric field caused by the presence of an additional carrier in a second well can itself be sufficient to forbid tunneling. Thus, a carrier will readily tunnel from well This embodiment will now be discussed in greater 45 1 into a depleted level in well 2, but that same carrier cannot tunnel back into well 1 except through inelastic channels, because now the levels no longer line up.

> For this self-generated field modification to be useful. it is necessary that the resonant peaks at the given operating temperature be relatively sharp. That is, the well dimensions should preferably be smaller than those necessary, at the operating temperature, or any resonant tunneling gain. For example, wells of appropriate dimensions for operation at room temperature will show such effects if operated at 77K or at 4K. The smaller wells mean that the field generated by the potential shift caused by the addition of one carrier will be greater.

> These self-generated field effects have other uses also. For example, consider the four-well structure shown in FIG. 17. A field plate or other bias connection is used to define a reference voltage  $V_0$  for well 3. The wells are tailored such that tunneling occurs from well 1 to well 3 only when  $V_3$  equals  $V_0$ ; tunneling occurs from well 2 to well 3 only when V<sub>3</sub> equals V<sub>0</sub> plus E, i.e., when the potential of well 3 has been modified by the presence of one electron; tunneling occurs from well 3 to well 4 only when well 3 has a potential V<sub>3</sub> equals  $V_0$  plus 2E. Input Signal A supplies carriers tun

15 16

neling into well 1, and input signal B supplies carriers tunneling into well 2, and an output contact retrieves an output signal C from well.

Thus, this primitive complex of wells provides an AND gate.

Other Boolean primitives are easily created. For example, in the same layout of wells, if we redefine the well couplings such that the tunneling occurs from well 1 to well 3 when  $V_3$  equals  $V_0$ , from well 2 to well 3 when  $V_3$  equals  $V_0$ , and from well 3 to well 4 when  $V_3$  10 equals V<sub>0</sub> plus E, we now have an OR gate. These couplings can be used to configure all primitive Boolean algebraic logic cells and more. In this regime, where self-generated fields are sufficient to disrupt tunneling, a problem may be caused by the presence of excess carri- 15 ers in a well. That is, if the coupling between wells A and B is designed to admit resonant tunneling when well A is populated and well B is not, tunneling may be disrupted if well A has two states populated rather than merely one. However, in such cases, the 2-carrier popu- 20 lation must have been created inelastically. Moreover, inelastic tunneling will provide a reset mechanism even-

A further family of the embodiments of the present invention utilize vertical tunneling. An attraction of 25 such structures is that extremely small dimensions, with extremely good interface quality are easier to achieve in the vertical dimension then in the lateral dimension.

A key feature of such embodiments is that the spacing of energy states in the well is in general defined by the 30 volume of the well. Thus, for a given well volume the well may be configured as a thin flat box rather than a roughly cubic box. In this case, two of the momentum components would be quantized with extremely closely spaced values, and the third component would be quantized with extremely widely spaced allowable momentum values.

Such embodiments are shown in FIGS. 19 through 20. Again, the wells 604-608 are preferably made of a first semiconductor and the barrier medium 612 is preferably made of a second, wider-band gap semiconductor. Gallium arsenide and AlGaAs are preferable for these two semiconductors. Current flows from n+electrode 602 to metal electrode 610 only if the potentials of row line 616 and column line 614 permit levels of 45 well 606 to line up with levels of wells 604 and 68, as discussed above.

Thus, the present invention provides the above-mentioned objects, as well as numerous other techincal advantages in accordance with the foregoing description. As will be apparent to those skilled in the art, the present invention is a pioneering invention, and can be modified with an immense variety of modification and variations. For example, Si wells can be used in an SiO<sub>2</sub> barrier medium, or other semiconductor/semiconductor or semiconductor/insulator systems can be used, in place of the preferred GaAs/AlGaAs materials system. The scope of the present invention is not limited except as set forth in the accompanying claims.

What is claimed is:

1. A process for fabricating quantum-well devices, comprising the steps of:

providing a substrate;

providing first and second epitaxial layers of a first semiconductor material on said substrate,

said first layer being doped to a concentration of at least 1E17 per cubic centimeter and being at least 200 nm thick,

and said second layer comprising a dopant concentration no greater than 5E16 per cubic centimeter and a thickness less than 300 Angstroms;

anisotropically etching trenches in a first pattern through said second layer but not entirely through said first layer;

epitaxially growing a second semiconductor material, which has a wider bandgap than said first semiconductor material and is approximately lattice-matched to said first semiconductor material, to substantially fill said trenches;

anisotropically etching trenches in a second pattern through both said first layer and said second layer into said substrate;

epitaxially growing said second semiconductor material, to substantially fill said second trenches; and forming metallization to configure a desired circuit function;

wherein said first and second patterned trench etches jointly define a plurality of quantum wells within isolated portions of said second layer,

and wherein said second trench etch defines interconnections of said quantum wells within said first layer.

2. A process for fabricating quantum-well devices, comprising the steps of:

providing a substrate;

providing first and second epitaxial layers of a first semiconductor material on said substrate,

said first layer being doped to a concentration of at least 1E17 per cubic centimeter and being at least 200 nm thick,

and said second layer comprising a dopant concentration no greater than 5E16 per cubic centimeter and a thickness less than 300 Angstroms;

anisotropically etching trenches in a first pattern through both said first layer and said second layer into said substrate;

epitaxially growing a second semiconductor material, which has a wider bandgap than said first semiconductor material and is approximately latticematched to said first semiconductor material, to substantially fill said trenches;

anisotropically etching trenches in a second pattern through said second layer but not entirely through said first layer;

epitaxially growing said second semiconductor material, to substantially fill said second trenches; and forming metallization to configure a desired circuit function;

wherein said first and second patterned trench etches jointly define a plurality of quantum wells within isolated portions of said second layer,

and wherein said first trench etch defines interconnections of said quantum wells within said first semiconductor layer.

3. A process for fabricating quantum-well devices, comprising the steps of:

providing a substrate;

providing first and second epitaxial layers of a first semiconductor material on said substrate, and a third epitaxial layer of a third semiconductor material which has a wider bandgap than said first semiconductor material and is approximately latticematched to said first semiconductor material,

said first layer being doped to a concentration of at least 1E17 per cubic centimeter and being at least 200 nm thick,

said second layer comprising a dopant concentration no greater than 5E16 per cubic centimeter and a thickness less than 300 Angstroms;

said third layer being less than 50 Angstroms thick and interposed between said first and second 5 lavers:

anisotropically etching trenches in a first pattern through said second layer but not entirely through said first layer;

epitaxially growing a second semiconductor material, 10 which has a wider bandgap than said first semiconductor material and is approximately latticematched to said first semiconductor material, to substantially fill said trenches;

through both said first layer and said second layer into said substrate:

epitaxially growing said second semiconductor material, to substantially fill said second trenches; and forming metallization to configure a desired circuit 20

wherein said first and second patterned trench etches jointly define a plurality of quantum wells within isolated portions of said second layer,

and wherein said second trench etch defines interconnections of said quantum wells within said first layer.

4. A process for fabricating quantum-well devices, comprising the steps of:

providing a substrate:

providing first and second epitaxial layers of a first semiconductor material on said substrate, and a third epitaxial layer of a third semiconductor material which has a wider bandgap than said first semiconductor material and is approximately latticematched to said first semiconductor material,

said first layer being doped to a concentration of at least 1E17 per cubic centimeter and being at least 200 nm thick,

said second layer comprising a dopant concentration no greater than 5E16 per cubic centimeter and a thickness less than 300 Angstroms;

said third layer being less than 50 Angstroms thick layers;

anisotropically etching trenches in a first pattern through both said first layer and said second layer into said substrate;

epitaxially growing a second semiconductor material, 50 which has a wider bandgap than said first semiconductor material and is approximately latticematched to said first semiconductor material, to substantially fill said trenches;

anisotropically etching trenches in a second pattern through said second layer but not entirely through said first layer;

epitaxially growing said second semiconductor material, to substantially fill said second trenches; and forming metallization to configure a desired circuit function;

wherein said first and second patterned trench etches jointly define a plurality of quantum wells within isolated portions of said second layer,

and wherein said first trench etch defines interconnections of said quantum wells within said first semiconductor laver.

5. The process of claim 1, wherein said substrate anisotropically etching trenches in a second pattern 15 comprises a semi-insulating III-V compound semicon-

ductor.

6. The process of claim 1, wherein said second semiconducting material comprises a carrier concentration of less than 1E16 per cubic centimeter.

7. The process of claim 1, wherein said first semiconducting material is GaAs.

8. The process of claim 1, wherein said second semiconducting material comprises AlGaAs.

9. The process of claim 2, wherein said substrate comprises a semi-insulating III-V compound semicon-

10. The process of claim 2, wherein said second semiconducting material comprises a carrier concentration of less than 1E16 per cubic centimeter.

11. The process of claim 2, wherein said first semiconducting material is GaAs.

12. The process of claim 2, wherein said second semiconducting material comprises AlGaAs.

13. The process of claim 3, wherein said substrate 35 comprises a semi-insulating III-V compound semicon-

14. The process of claim 3, wherein said second semiconducting material comprises a carrier concentration of less than 1E16 per cubic centimeter.

15. The process of claim 3, wherein said first semiconducting material is GaAs.

16. The process of claim 3, wherein said second semiconducting material comprises AlGaAs.

17. The process of claim 4, wherein said substrate and interposed between said first and second 45 comprises a semi-insulating III-V compound semiconductor.

> 18. The process of claim 4, wherein said second semiconducting material comprises a carrier concentration of less than 1E16 per cubic centimeter.

19. The process of claim 4, wherein said first semiconducting material is GaAs.

20. The process of claim 4, wherein said second semiconducting material comprises AlGaAs.